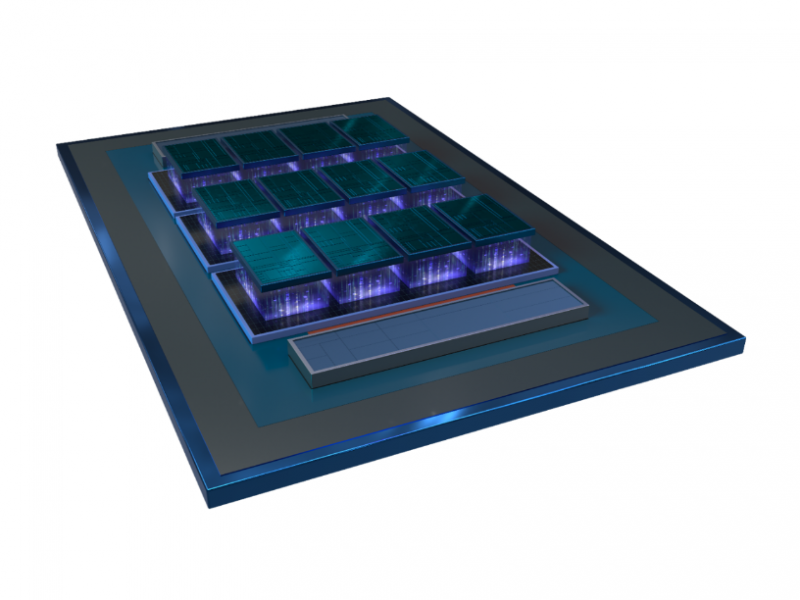

步入 AI 时代,在制程技术之外,先进封装已经成为半导体行业的「新宠」。何为先进封装?简单来说,就是把多个芯片集成到同一设备中的技术。

步入 AI 时代,在制程技术之外,先进封装已经成为半导体行业的「新宠」。何为先进封装?简单来说,就是把多个芯片集成到同一设备中的技术。

在 AI 芯片的制造过程中,采用先进封装的优势是多方面的:首先,AI 芯片需要处理大量数据,先进封装能够实现芯片间的高速互连,从而提升数据传输速度、提高数据吞吐量;其次,AI 芯片的结构复杂,先进封装支持异构集成,可以将 CPU、GPU、NPU、I/O 等功能单元连接在一起妥善运行;第三,AI 芯片需要有极高的算力,先进封装可以改善系统密度,增加单个设备内的晶体管数量,同时也具有良好的可扩展性;最后,在采用先进封装的设备中,不同的芯片可以采用来自不同厂商的不同制程节点制造,既提升了灵活性,也有助于降低成本。

目前,业界主要的先进封装技术包括 TSMC 的 CoWoS 和 CoPoS,英特尔的 EMIB、Foveros 和 Foveros Direct 等等。芯片设计公司对先进封装的需求不断水涨船高,而 TSMC 的产能有限,这为其它厂商带来了巨大机遇。近期,英特尔在先进封装领域进展颇多。3 月,英特尔宣布位于马来西亚槟城的先进封装工厂将于今年晚些时候全面投产;据《连线》报道,谷歌和亚马逊正在与英特尔就先进封装代工进行洽谈。

产能之外,英特尔的先进封装在技术水平和对 AI 架构的支持上同样具备相当的竞争力。例如,就 2.5D 封装而言,其它厂商采用的方式是在所有芯片下方单独放置一层硅中介层,通过中介层实现互连。然而,一旦中介层的尺寸超过一定限度,其制造成本和难度就会飙升,随着 AI 芯片变得越来越大,这一问题日益凸显。

英特尔的 EMIB(嵌入式多芯片互连桥接)技术则「另辟蹊径」,先在晶圆上制造作为硅桥的芯片,因为面积相对较小,晶圆利用率可达 90%,帮助客户降低成本、提高效率。这些硅桥随后被嵌入到大尺寸有机矩形面板中,大面板再被分割成若干矩形基板。随后,将各种功能单元连接到基板上,硅桥只在需要的地方提供局部的高密度互连。EMIB 的演进版本 EMIB-T 则增加了硅通孔,能够实现垂直电源传输,并降低直流和交流噪声带来的信号串扰。

相比之下,基于硅中介层的解决方案则需要与整个封装的尺寸相匹配,对于尺寸大于 8 倍光罩复合体的大型设备来说,这会将晶圆利用率降低至 60%,同时,中介层必须贴附到基板上,会占用大量空间。

换言之,因为硅桥直接嵌入基板内部,EMIB 和 EMIB-T 技术能够随着封装尺寸的增大不断扩展,这是硅中介层无法实现的。目前,英特尔代工能够实现的最大芯片复合体尺寸约为光罩尺寸的 6 倍,到 2026 年底,这一数字将达到 8 倍以上(约 6800 平方毫米),到 2028 年,将进一步增加到光罩尺寸的 12 倍以上(约 10000 平方毫米),容纳 16 个或更多的 HBM4/HBM5 堆叠和 30 个或更多的 EMIB-T 硅桥。

英特尔代工还提供其它的先进封装技术,共同组成一套完备的产品组合:Foveros-S 是英特尔版本的硅中介层解决方案;Foveros-R 提供基于重布线层的中介层,具有更大的灵活性,有助于客户进一步优化成本;Foveros Direct 则通过混合键合技术,将芯片垂直堆叠,实现真正的 3D 封装。此外,EMIB 与 Foveros 系列技术相结合,可实现 3.5D 集成。在此架构中,多个垂直堆叠的芯片组通过 EMIB 进行横向互连,从而为构建更大、更快、更高效的多芯片 AI 和系统提供了可扩展的模块化平台。

之所以英特尔先进封装技术的前景值得期待的,除了上述技术领域的创新,还有公司文化层面的转变。客户可以选择在制造流程的任何环节使用英特尔的服务,可以从另一家供应商购买晶圆,然后到英特尔的晶圆厂进行封装,也可以先找另一家供应商代工传统的芯片封装,再和英特尔合作进行先进封装。从「不接受其它代工厂的晶圆」,到「将满足客户需求放在首位」,英特尔已经开始理解代工厂与客户建立信任关系的真谛所在。

来源:互联网